帶隙與電流基準(zhǔn)電路在模擬集成電路設(shè)計中的應(yīng)用

模擬集成電路設(shè)計中,帶隙與電流基準(zhǔn)電路是實現(xiàn)高精度、高穩(wěn)定性的關(guān)鍵模塊。它們在電源管理、數(shù)據(jù)轉(zhuǎn)換器、傳感器接口等多種應(yīng)用中,提供不隨溫度和工藝變化而顯著漂移的參考電壓和電流。本文將系統(tǒng)探討帶隙基準(zhǔn)電路和電流基準(zhǔn)電路的工作原理、設(shè)計方法及其在集成電路中的實現(xiàn)。

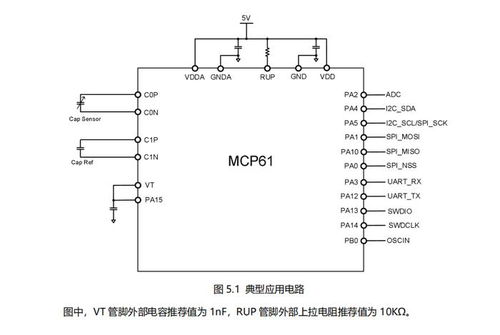

帶隙基準(zhǔn)電路的核心思想是利用半導(dǎo)體材料的帶隙電壓特性,產(chǎn)生一個與溫度無關(guān)的穩(wěn)定參考電壓。典型的帶隙基準(zhǔn)電路通常由雙極型晶體管(BJT)或MOSFET構(gòu)成,通過巧妙地組合正溫度系數(shù)和負(fù)溫度系數(shù)的電壓,實現(xiàn)溫度補(bǔ)償。例如,利用ΔVBE的正溫度系數(shù)和VBE的負(fù)溫度系數(shù),在特定溫度點(如27°C)附近,兩者相互抵消,從而得到一個約為1.25V的穩(wěn)定輸出電壓。設(shè)計時需考慮工藝偏差、電源電壓變化和噪聲抑制,常見技術(shù)包括使用運(yùn)放反饋、 curvature補(bǔ)償和 trimming 電路。

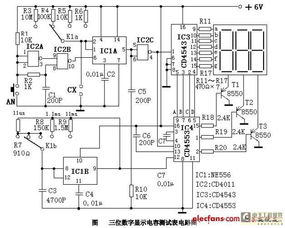

電流基準(zhǔn)電路則基于帶隙基準(zhǔn)電壓,通過電阻或晶體管電路轉(zhuǎn)換為穩(wěn)定的參考電流。在CMOS工藝中,常采用帶隙電壓與電阻結(jié)合的方式,生成與電源和溫度無關(guān)的電流。例如,利用帶隙輸出電壓VREF和精準(zhǔn)電阻R,產(chǎn)生IREF = VREF / R。電流鏡結(jié)構(gòu)被廣泛用于復(fù)制和分配基準(zhǔn)電流,確保多個電路模塊的一致性。設(shè)計電流基準(zhǔn)時,需關(guān)注電阻的溫度系數(shù)、匹配精度以及電源抑制比(PSRR),以最小化外部干擾。

在集成電路設(shè)計中,帶隙與電流基準(zhǔn)電路的集成需考慮面積、功耗和噪聲性能。現(xiàn)代工藝下,低壓帶隙電路和亞閾值設(shè)計成為趨勢,以適應(yīng)低功耗應(yīng)用。自校準(zhǔn)和數(shù)字修調(diào)技術(shù)被引入,以應(yīng)對工藝變化,提高量產(chǎn)良率。

帶隙與電流基準(zhǔn)電路是模擬集成電路的基石,其設(shè)計精粹在于平衡溫度穩(wěn)定性、工藝魯棒性和性能指標(biāo)。隨著工藝節(jié)點的進(jìn)步,這些電路將繼續(xù)演進(jìn),支持更復(fù)雜、高效的電子系統(tǒng)。

如若轉(zhuǎn)載,請注明出處:http://www.sitelove.cn/product/34.html

更新時間:2026-01-10 04:11:20