數(shù)字集成電路設(shè)計(jì) 原理、流程與應(yīng)用

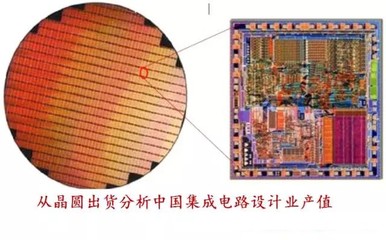

數(shù)字集成電路是現(xiàn)代電子系統(tǒng)的核心,將邏輯門(mén)、存儲(chǔ)單元和互連結(jié)構(gòu)集成在單一芯片上,廣泛應(yīng)用于計(jì)算機(jī)、通信設(shè)備和消費(fèi)電子產(chǎn)品。本書(shū)《數(shù)字集成電路設(shè)計(jì)》系統(tǒng)介紹了從基礎(chǔ)理論到實(shí)際設(shè)計(jì)的完整知識(shí)體系。

第一章闡述數(shù)字集成電路的基本概念,包括布爾代數(shù)、CMOS工藝和邏輯家族。讀者將理解晶體管如何構(gòu)成基本門(mén)電路,以及電壓、電流和時(shí)序在數(shù)字系統(tǒng)中的關(guān)鍵作用。

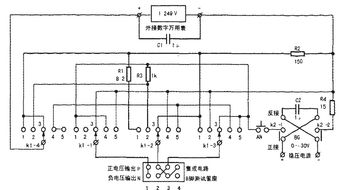

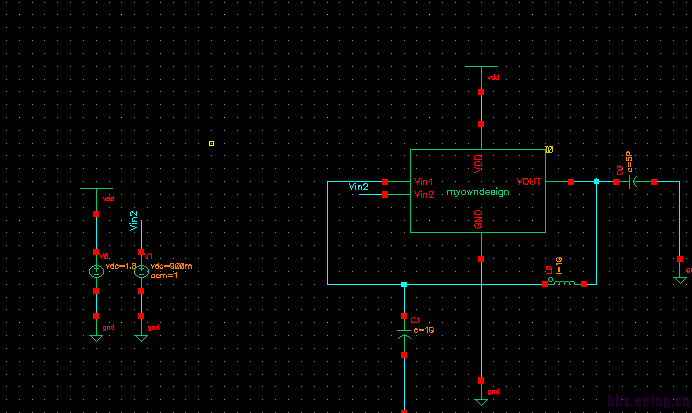

第二章聚焦設(shè)計(jì)方法學(xué),涵蓋自上而下的設(shè)計(jì)流程:從系統(tǒng)規(guī)范、RTL編碼到邏輯綜合和物理實(shí)現(xiàn)。重點(diǎn)討論硬件描述語(yǔ)言(如Verilog和VHDL)的應(yīng)用,以及仿真、驗(yàn)證和測(cè)試策略。

第三章深入分析時(shí)序和功耗問(wèn)題。時(shí)鐘分配、建立保持時(shí)間、動(dòng)態(tài)與靜態(tài)功耗管理等主題被詳細(xì)解釋?zhuān)o以實(shí)際設(shè)計(jì)案例,幫助讀者掌握優(yōu)化電路性能的技巧。

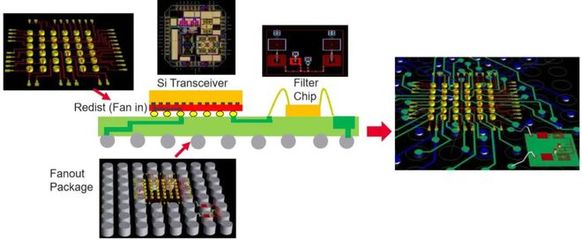

第四章介紹先進(jìn)技術(shù),如低功耗設(shè)計(jì)、可測(cè)試性設(shè)計(jì)和系統(tǒng)級(jí)芯片(SoC)集成。隨著工藝節(jié)點(diǎn)縮小至納米級(jí),本書(shū)還討論了信號(hào)完整性、互連延遲和可靠性挑戰(zhàn)。

最后一章展望未來(lái)趨勢(shì),包括3D集成、人工智能加速器和量子計(jì)算接口。本書(shū)適合電子工程專(zhuān)業(yè)學(xué)生和從業(yè)工程師,結(jié)合理論與實(shí)踐,為讀者奠定堅(jiān)實(shí)的數(shù)字IC設(shè)計(jì)基礎(chǔ)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.sitelove.cn/product/13.html

更新時(shí)間:2026-01-10 09:13:38